8051 IP-Core in VHDL

Oft werden in FPGA-Designs Prozessoren verwendet.

Hierzu werden von zahlreichen Herstellern kommerzielle und auch freie Versionen angeboten, meistens geht hier der Trend zu leistungsfähigen 32 Bit Prozessoren.

Oft wird die Leistungsfähigkeit solcher Prozessoren jedoch nicht benötigt, ein kompakter 8 Bit Prozessor

mit geringem Resourcenverbrauch und keinen bzw. geringen Anforderungen an zusätzliche Hardware ist in solchen Fälle die bessere Wahl.

Für diese Fälle haben wir unsere L52 Serie mit 8051 kompatiblen Befehlssatz entwickelt.

L5216Tiny:

1 x 16Bit DPTR,

8 Interrups, 2 Prioritäten,

256 Byte IDATA, 64k CODE, 64k XDATA,

50MIPS,

ca. 1720 LEs im Intel FPGAs (CPU).

L5216:

2 x 24Bit DPTR,

16 Interrups, 8 Prioritäten,

256 Byte IDATA, 64k CODE, 16M XDATA,

Stack im XDATA Memory.

"Extended" Stackpointer (16 Bit)

50MIPS,

ca. 2300 LEs im Intel FPGAs(CPU).

L5224:

2 x 24Bit DPTR,

16 Interrups, 8 Prioritäten,

256 Byte IDATA, 16M CODE, 16M XDATA,

Stack im XDATA Memory.

"Extended" Stackpointer (16 Bit)

"Extended" Befehlssatz für 24 Bit Adressraum.

50MIPS,

ca. 2750 LEs im Intel FPGAs(CPU).

Alle Typen sind in einer "single clock" und einer "dual clock" Version erhältlich.

Bei der "single clock" Version wird nur ein einziger "Clock" benötigt, allerding verlängern sich alle Befehle die lesend auf das IDATA Ram zugreifen um einen "Clock". So benötigt z.B. ein "add A, R1" zwei anstelle von einem "Clock" (40ns anstelle von 20ns).

Bei der "dual clock" Version wird ein zwei Phasen "Clock" benötigt. Dieser ist der Regel in modernen FPGAs mit einer PLL einfach zu erzeugen. Für die Befehlsausführung wird bei den allermeisten Befehlen ein "Clock" (20ns) pro Byte Befehlslänge benötigt.

In der Tabelle finden Sie die Ausführungszeiten für den L5224.

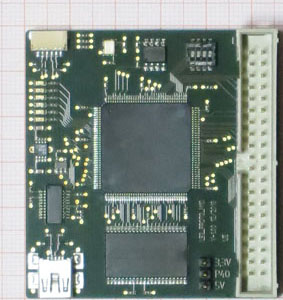

Mit unserem kompakten Eval-Board können Sie sich auf einfache und preiswerte Weise von der Leistungsfähigkeit des L5216 oder L5224 Cores überzeugen.

Als Debugger ist der Keil MON51 bzw. MON390 vorinstalliert.

Bei Interesse setzen Sie sich bitte mit uns in Verbindung